Laying Groundwork to Prototype Lightning-Fast Computer Chip

With third award from DARPA and multiuniversity collaboration, Ali Akoglu and his team are helping push processing power toward a million-times-faster future.

Ali Akoglu, professor of electrical and computer engineering and the BIO5 Institute at the University of Arizona, has received a third award, $393,000, from the Defense Advanced Research Projects Agency, or DARPA, supporting his work on computer chips capable of lightning-fast processing power.

Chips, or microprocessors, are the foundation for most of today’s electronics — from supercomputers to smart phones to the technology for self-driving vehicles.

In a world connecting more and more computing equipment performing highly complex tasks and demanding greater and greater processing speeds, “this will enable effective communication systems designed for future generations,” Akoglu said. “This intelligence will be on all of our network devices.”

With this award from the DARPA program – Processor Reconfiguration for Wideband Sensor Systems, or PROWESS – Akoglu and collaborators from multiple universities are mapping out plans for a computer chip with software that makes decisions in 50 nanoseconds, almost a million times faster than the processing power of traditional computer chips.

Akoglu said previous research indicates it is possible to make a lightning-fast chip, but translating theory into a physical prototype will be difficult, adding that 50 nanoseconds is quite aggressive.

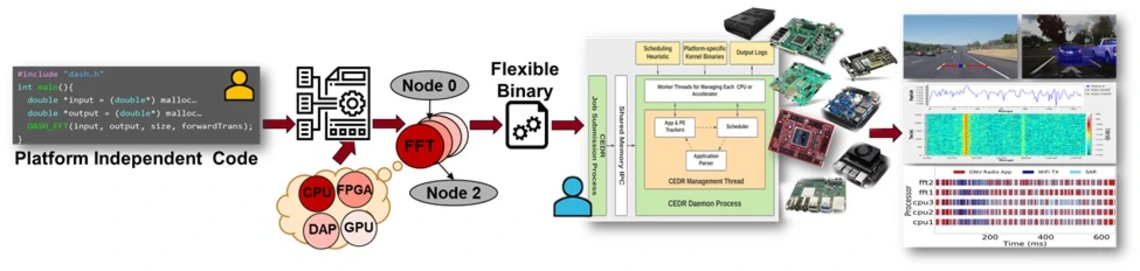

Akoglu’s team is working with researchers from Arizona State University, the University of Wisconsin and the University of Michigan. Phase 1 of the project, “Dynamic Runtime Domain-Focused Software-Reconfigurable Heterogeneous (DR-DASH) Processor,” consists of a highly adaptable chip housing an autonomous runtime manager.

“Michigan is handling the chip fabrication, ASU is developing the algorithm, and then my group is kind of the glue,” said Akoglu.

Akoglu is the principal investigator of the team focusing on the software of the DR-DASH project. He is working closely with University of Wisconsin researchers.

“The challenge is to be able to support hundreds of applications on the system,” he said. “There’s so many algorithms running at the same time.”

Laying the groundwork, researchers in Akoglu’s Reconfigurable Computing Laboratory developed a runtime manager called CEDR (Compile Integrated Domain Specific System on Chip Runtime) for two other DARPA-funded programs – Domain Specific System on Chip (DSSoC) and Space-Based Adaptive Communications Node (Space-BACN). Runtime managers in computer chips allocate resources for starting, stopping and monitoring multiple applications.

CEDR’s autonomous decision-making lends significantly to faster computing time, and Akoglu’s team plans to incorporate the runtime manager onto the DR-DASH chip.

If DARPA approves Phase 2, Akoglu’s team will receive an additional $668,000 to lead software integration on the chip prototype.

“In the context of the Internet of Things, you will have these highly capable communication nodes in your cellphone, on your network devices, or even in health care with your wearable devices,” he said. “Anywhere that communication is key – these processes will be handled autonomously.”